Ahora estás siguiendo a

Error al seguir a usuario.

Este usuario no permite que los usuarios lo sigan.

Ya estás siguiendo a este usuario.

Tu plan de membresía solo permite 0 seguimientos. Mejora tu membresía aquí.

Dejaste de seguir correctamente a

Error al dejar de seguir al usuario.

Has recomendado exitosamente a

Error al recomendar al usuario.

Algo salió mal. Por favor, actualiza la página e intenta de nuevo.

Email verificado correctamente.

alexandria,

egypt

Aquí son las 5:58 a. m.

Se unió el diciembre 7, 2022

0

recomendaciones

Mohamed M.

@Majiidd

0,0

0,0

100%

100%

alexandria,

egypt

N/A

Trabajos finalizados

N/A

Dentro del presupuesto

N/A

A tiempo

N/A

Tasa de recontratación

Verilog/SV/VHDL RTL coding | FPGA | ASIC | VLSI

Contacta Mohamed M. sobre tu trabajo

Inicia sesión para comentar cualquier detalle por chat.

Portafolio

Portafolio

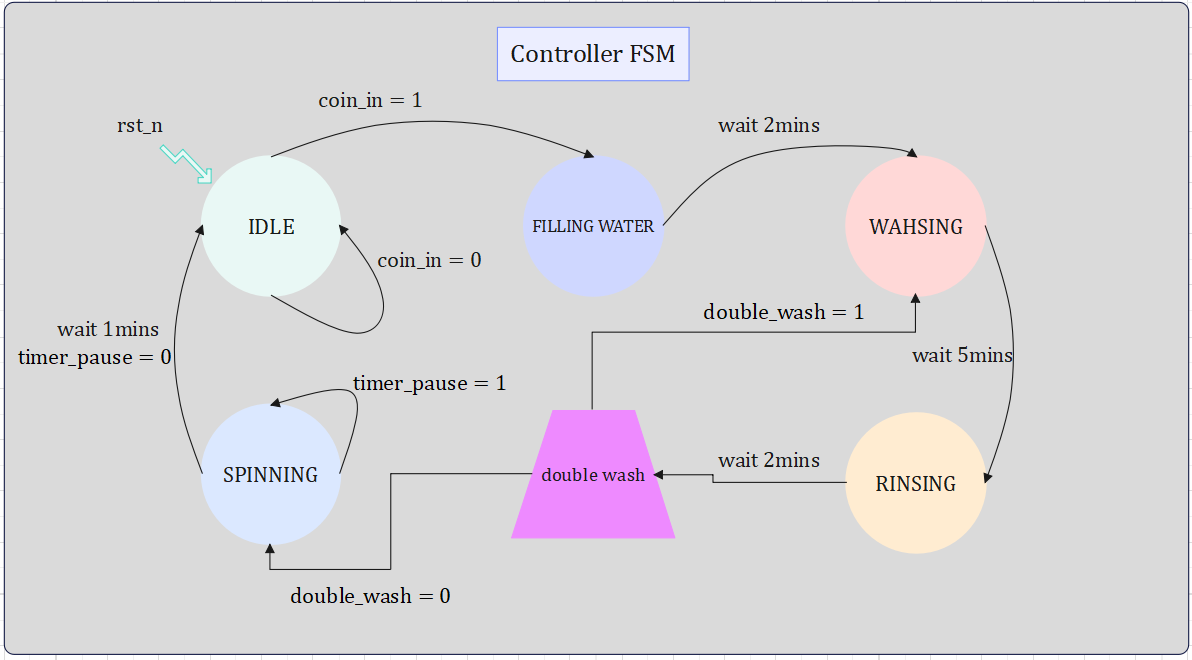

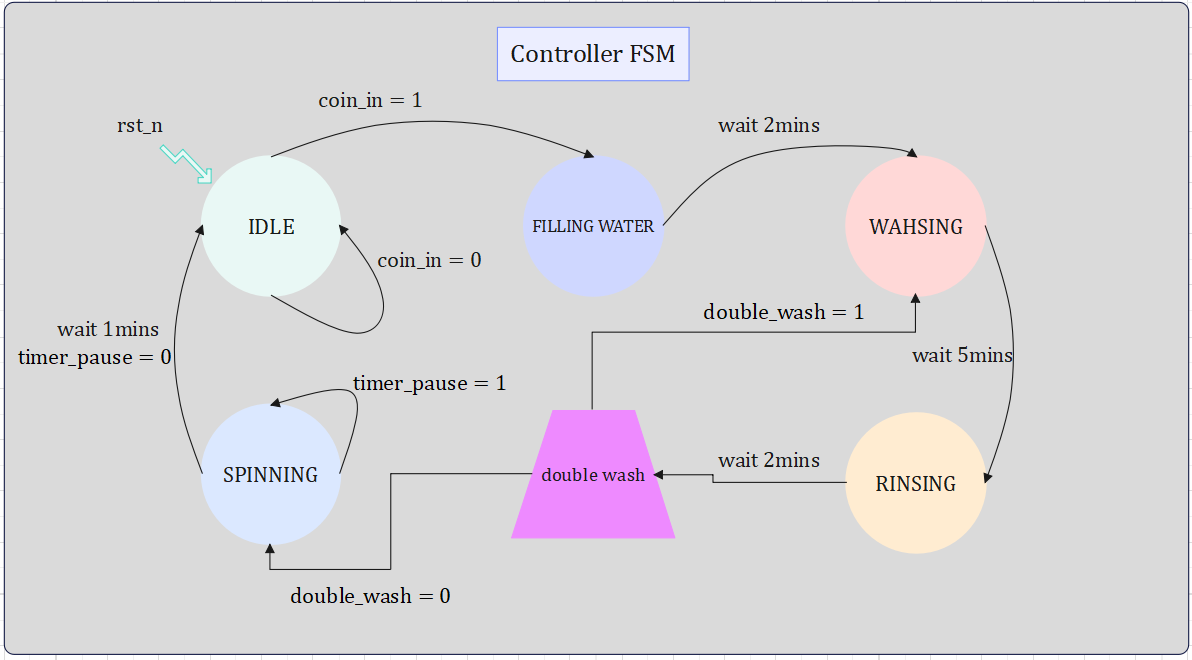

Washing Machine Controller, using Verilog HDL.

Washing Machine Controller, using Verilog HDL.

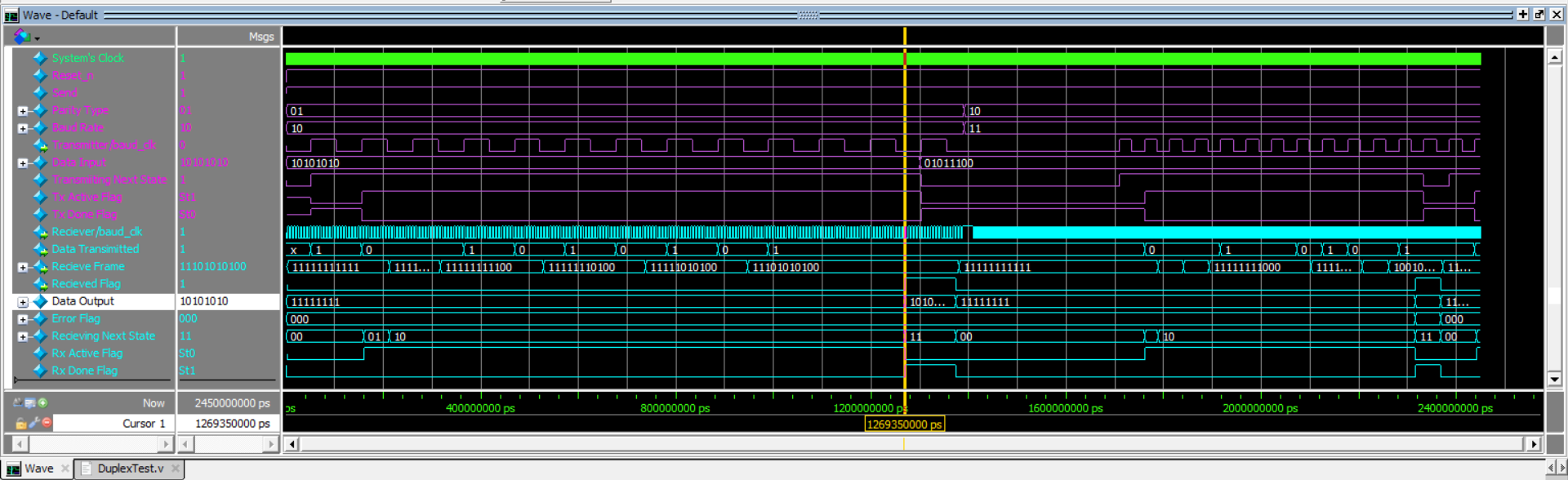

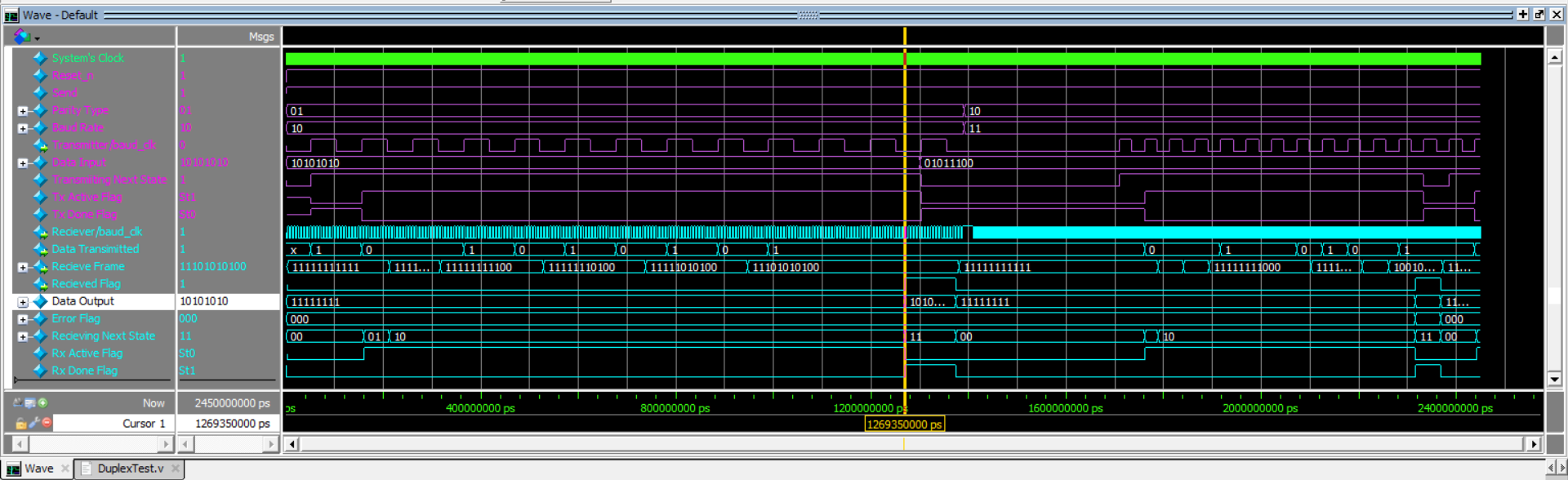

Full UART implementation using Verilog HDL

Full UART implementation using Verilog HDL

Full UART implementation using Verilog HDL

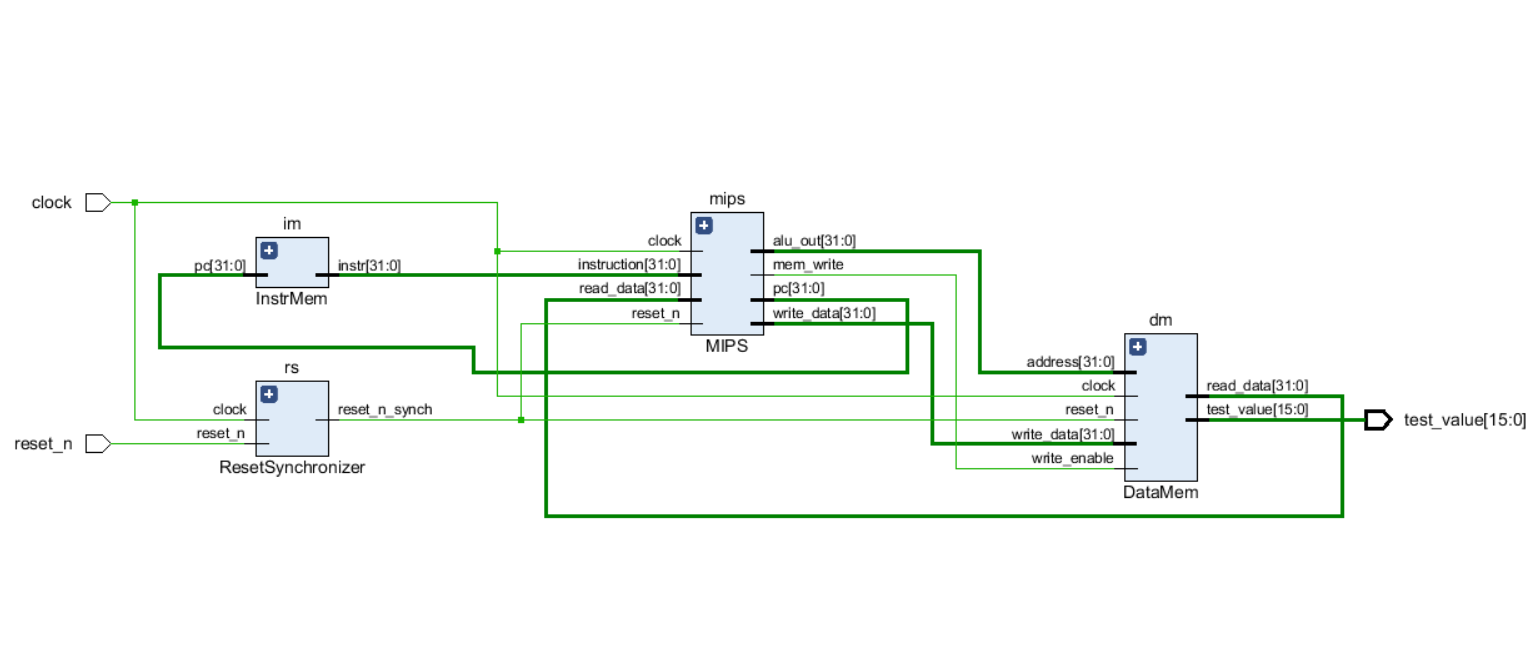

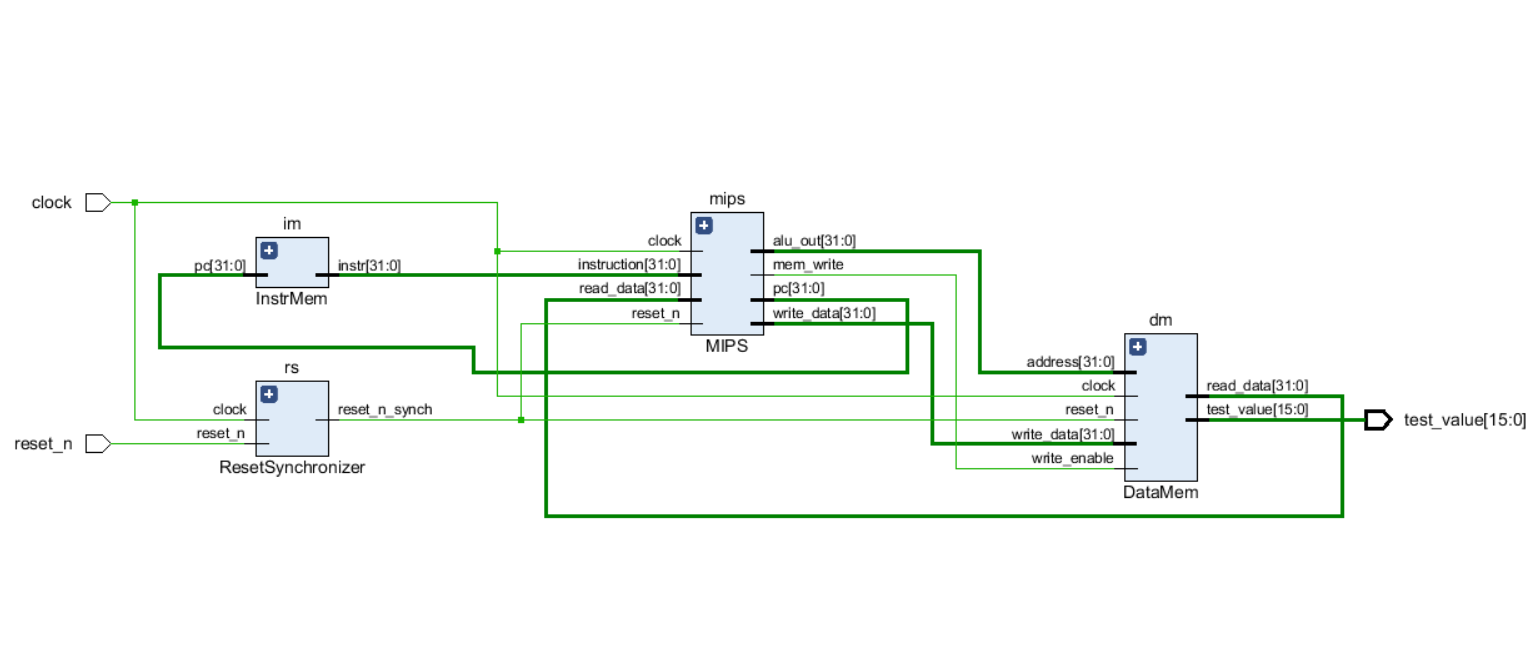

Implementation of 32-bit MIPS-processor using SystemVerilog

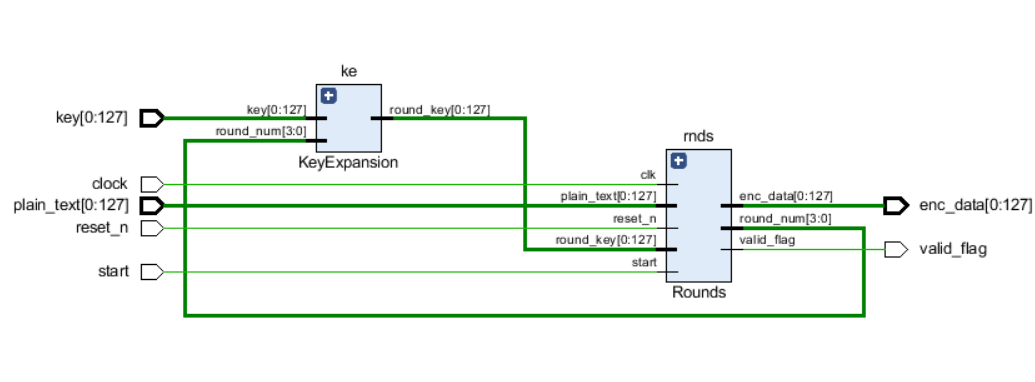

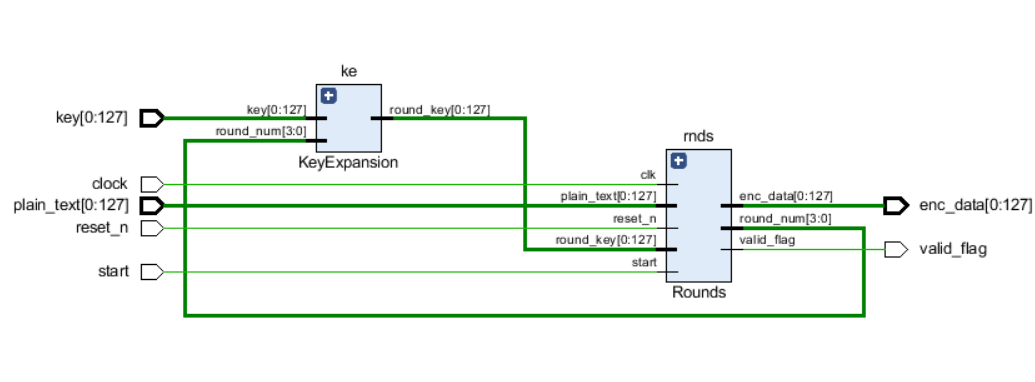

Advanced Encryption Standard (AES) modelling, using Verilog

Washing Machine Controller, using Verilog HDL.

Washing Machine Controller, using Verilog HDL.

Full UART implementation using Verilog HDL

Full UART implementation using Verilog HDL

Full UART implementation using Verilog HDL

Implementation of 32-bit MIPS-processor using SystemVerilog

Advanced Encryption Standard (AES) modelling, using Verilog

Comentarios

Cambios guardados

¡No hay comentarios para ver aquí!

Experiencia

Digital IC Design and Verfication

mar 2022 - Presente

◦ Efficient Synthesizable RTL coding: using Verilog/SystemVerilog HDLs

◦ Computer Architecture: Undersatnding of the under-hood of the computer by studying the MIPS processor architecture

and designing it by SystemVerilog HDL.

◦ Verification: Understanding of the basic concepts of verification using SystemVerilog HDL.

Digital IC Design with FPGA

ago 2022 - nov 2022 (3 meses, 1 día)

◦ Efficient Synthesizable RTL coding: using Verilog HDL, Self-test test benches.

◦ Synthesis and implementation: used Xilinx ISE to implement the design on Spartan-6, I/O

planning layout using the PlanAhead tool, tested the design with multiple clock domains and applied to time

constraints.

◦ Acceleration FPGA Design: used Vivado IDE to implement the design on the Zynq-7000 board, used the logic analyzer to debug the design and created IP then used the IP integrator to create a block design.

Educación

Bachelor degree of Electronics and Electrical Communication Engineering

(4 años)

Calificaciones

Digital Design with FPGA

NajahNow, One Lab, Zewail City

2022

- Efficient Synthesizable RTL coding: using Verilog HDL, verified by Self-test test-benches.

- HDL Synthesis and implementation on FPGA: used Xilinx ISE to implement the design on Spartan-6 FPGA, I/O planning layout for pin assignment using PlanAhead tool, tested the design with multiple clock domains, and applied timing constraints.

- Acceleration FPGA Design: used Vivado IDE to implement the design on the Zynq-7000 board.

Contacta Mohamed M. sobre tu trabajo

Inicia sesión para comentar cualquier detalle por chat.

Verificaciones

Principales habilidades

Explorar freelancers similares

Explorar galerías similares

¡Invitación enviada correctamente!

¡Gracias! Te hemos enviado un enlace para reclamar tu crédito gratuito.

Algo salió mal al enviar tu correo electrónico. Por favor, intenta de nuevo.

Cargando visualización previa

Permiso concedido para Geolocalización.

Tu sesión de acceso ha expirado y has sido desconectado. Por favor, inica sesión nuevamente.